Sistema Combinacional o Lógica Combinacional (Parte 3)

Autor: Rubén San Martín. Centro de Ingeniería Eléctrica y Sistemas (CESICE). FIIIDT.

Esta tercera parte va dirigida hacia los circuitos Decodificadores, que forman parte de los Circuitos de Comunicación, estos transmiten información por una línea de código como para codificar, decodificar o modificar la estructura de dicha información.

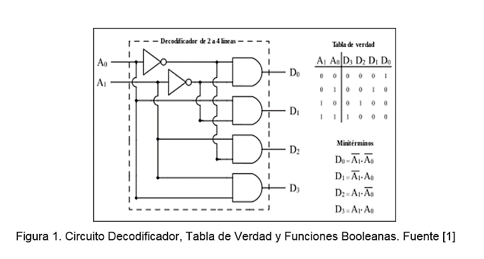

Un Decodificador o descodificador es un circuito combinacional, cuya función es inversa a la del Codificador, esto se refiere a que, convierte un código binario de entrada (natural, BCD, etc.) de N bits de entrada y M líneas de salida (N puede ser cualquier entero y M es un entero menor o igual a 2N), tales que cada línea de salida será activada para una sola de las combinaciones posibles de entrada. Estos circuitos, normalmente, se suelen encontrar como decodificador / demultiplexor. Esto es debido a que un demultiplexor puede comportarse como un decodificador.

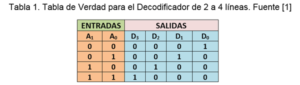

Si por ejemplo se tiene un decodificador de 2 entradas con 22 = 4 salidas, su funcionamiento sería el que se indica en la Tabla 1, donde se considera que las salidas se activen con un » 1 » lógico:

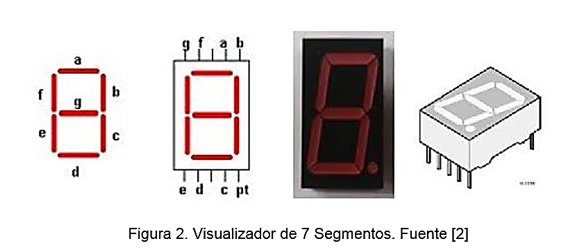

Un tipo de decodificador muy empleado es el de siete segmentos. Este circuito decodifica la información de entrada en BCD a un código de siete segmentos adecuado para que se muestre en un Visualizador Display de siete segmentos como el que se muerta en la Figura 2.

Aplicaciones del Decodificador: La función principal de un Decodificador, es la de direccionar espacios de memoria. Un decodificador de N entradas puede direccionar 2N espacios de memoria. Por ejemplo, para poder direccionar 1kb de memoria necesitaría 10 bits, ya que la cantidad de salidas seria 210, igual a 1024. De esta manera, con 20 bits se tiene 220 que es 1Mb y con 30 bits tengo 230 que es 1Gb.

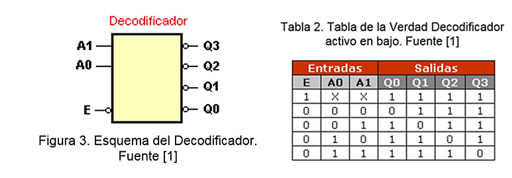

En un decodificador de 2 a 4 (se tienen 2 pines de entrada y 4 pines de salida). En la entrada se pone el código en binario (00, 01, 10, 11), que hará que se active sólo una salida de las cuatro posibles. Obsérvese la Figura 3, se puede ver que en la entrada E y en todas las salidas Q, hay una pequeña esfera o bolita. Esta esfera indica que la entrada (en el caso de E) y las salidas, son activas en bajo o “0” lógico.

Con esto se quiere decir que cuando se pone A0 = 0 y A1 = 0 y se está escogiendo la salida Q0, ésta tendrá un nivel de Voltaje bajo, mientras que todas las otras salidas (Q1, Q2 y Q3) estarán en nivel alto. De igual manera cuando la entrada E está en nivel bajo (activo en bajo), el decodificador está habilitado. Si está en nivel alto, el decodificador está inhabilitado y ninguna entrada en A0 y A1 tendrá efecto. Ver la Tabla 2.

Implementación de Funciones Lógicas con Decodificadores.

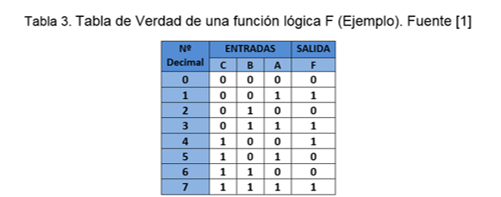

Una de las aplicaciones de los Decodificadores, es la posibilidad de ejecución de una ecuación booleana de funcionamiento correspondiente a una función lógica. Suponga, por ejemplo, la Tabla de Verdad de una función lógica F, véase es la Tabla 3.

La función lógica representada en la tabla es:

Para implementar dicha función utilizando un Decodificador, se debe seguir los siguientes procesos:

- Se emplea un decodificador del mismo o mayores números de líneas de entradas que de variables.

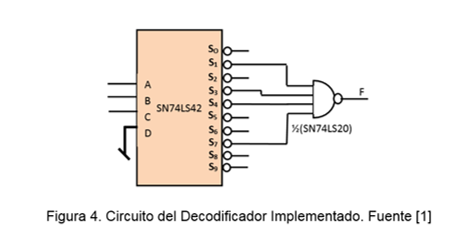

En este caso, se usa un decodificador de 4 a 10 líneas con las salidas activas en el nivel bajo, conectando a tierra la entrada de mayor peso.

- Se busca cada una de las salidas del decodificador que correspondan con las combinaciones de las variables de entrada que hacen “1” la salida de la tabla de verdad de la función F. En este caso:

- Para conseguir la suma de los términos de la función F se conectan todas las salidas del decodificador ya seleccionadas a una puerta lógica cuyo tipo dependerá del tipo de decodificador empleado. Esta puerta será:

- Compuerta OR para Decodificadores con salidas activas en Nivel Alto, ya que la función deberá ser activa siempre que se haga “1”, uno o varios de los términos que constituyen la función.

- Compuerta NAND para Decodificadores con salidas activas en el Nivel Bajo, ya que, al encontrarse negado cada termino activo de la función por el decodificador, la salida se deberá activar solo cuando uno o varios términos de la función valgan “0”.

En este caso, por partir de un decodificador activo en el nivel bajo, se emplea una compuerta NAND. La Figura 4 muestra el circuito final de la implementación.

Como se puede apreciar, si a la entrada aparece un valor que activa la función, por ejemplo, el 3 en decimal (011 en binario), en la salida S3 del decodificador se obtendrá un “0” (por ser un decodificador con salidas activas en nivel bajo). Sin embargo, cuando se introduce un “0” en la entrada de una NAND, aparecerá un “1”, activando la salida del circuito.

Si, por el contrario, en la entrada aparece una combinación de las que hacen “0” la función F, por ejemplo, el 5 (101), en la salida S5 del decodificador aparecerá un “0”, pero todas las entradas de la NAND estarán en “1”, por lo que en la salida del circuito habrá un “0”.

- En el caso de que una o varias de las combinaciones de la Tabla de Verdad que hacen “1” la salida de la función F no tuviera correspondencia con las salidas del decodificador, se añadirás compuertas que representarán las combinaciones correspondientes. Las salidas de estas compuertas serían llevadas, junto a la del circuito implementado a una compuerta OR final.

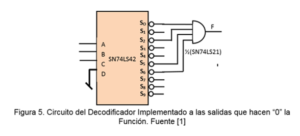

Otra forma de implementar un circuito con decodificadores es empleando el mismo decodificador y una compuerta AND, la diferencia, en este caso, es que se deben tomar las salidas del decodificador que hacen “0” la función F.

Los decodificadores simplifican mucho las funciones booleanas al igual que simplifican los circuitos realizados exclusivamente con compuertas lógicas, son de gran ayuda para integrar grandes funciones en circuitos pequeños. Para la cuarta parte de los Sistemas Combinacionales se hablará de los circuitos Multiplexores, cómo funcionan, para qué sirven y su lógica interna.

Bibliografía:

[1] Andrés Herrera (2016). Trabajo de Laboratorio Nº02: Diseño de Sistemas Lógicos Combinacionales en Media Escala de Integración (MSI). – Venezuela (Guía de Laboratorio de Sistemas Lógicos) Charallave: Universidad Nacional Experimental Politécnica “Antonio José de Sucre”, Ingeniería Mecatrónica.

[2] Área Tecnología (N). Display. Fecha de consulta: 13, octubre, 2020 desde https://www.areatecnologia.com/electronica/led-display.html

Contacto: rubensanmartin95@gmail.com