Desarrollo de un Sistema de Adquisición de Imágenes controlado por FPGA

Autores: Ramos Tomas, Rondón Hermes, Speranza Armando, Arellano Miguel. Centro de Ingeniería Eléctrica y Sistemas (CIES).FIIIDT.

Resumen

En este artículo se presentan los resultados parciales del desarrollo de un Sistema de Adquisición de Imágenes Digitales Georeferenciadas. El prototipo desarrollado es el control de un sensor de imágenes pancromático de 6.6Mpixeles, con tecnología basada en Semiconductor de Óxido Metálico Complementario (CMOS), controlado mediante una tarjeta de desarrollo comercial modelo DE2-70 de ALTERA basada en Arreglo de Compuertas Programables en Campo (FPGA). Asimismo, el sistema cuenta con un módulo de georeferenciación, basado en los datos obtenidos por una Unidad de Medidas Inerciales (IMU) y un GPS integrado, el cual genera las magnitudes de las variables inerciales para cada imagen capturada. Los datos de las imágenes, los del sistema de captura y los de georeferenciación son agrupados y estructurados en la FPGA para transmitirlos hacia una PC mediante un bus serial de alta velocidad, para su posterior almacenamiento en un formato de imagen estándar.

Palabras claves— FPGA, IMU/GPS, Sensor de Imagen CMOS, VHDL.

I. INTRODUCCIÓN

En la Fundación Instituto de Ingeniería (FII) se ejecutó un proyecto de investigación y desarrollo, que consistió en el diseño y desarrollo de un sistema de imágenes multiespectrales aerotransportado, para los fines de monitoreo remoto de recursos naturales, desastres y riesgos forestales, gestión municipal y urbana, entre otras aplicaciones. Un sistema de imágenes multiespectrales es, por definición, un sistema capaz de proporcionar información completa del espectro electromagnético de forma instantánea en cada píxel de la imagen capturada de una escena [1]. El principal componente de un sistema de imágenes digitales es la cámara, la cual está compuesta por un sensor de tecnología de Dispositivos de Carga Acoplada (CCD) o CMOS, con capacidad para captar las longitudes de onda del espectro visible y del infrarrojo cercano. El término aerotransportado se emplea debido a que estos sistemas están soportados sobre algún medio de transporte aéreo, bien sea un avión, un globo aerostático o un helicóptero. Asimismo, debido a que las imágenes captadas son una representación físico-territorial de algún terreno o área geográfica, y requieren de una serie de datos para su post procesamiento, estos sistemas cuentan con dispositivos de georeferenciación, los cuales generan medición de parámetros geográficos y de navegación, para asociarlos a cada imagen al momento de realizar las correcciones finales del sistema.

Por otra parte, los sistemas digitales de adquisición de imágenes se clasifican comúnmente en función del número de canales, tal como sigue: Sistema monocromático con un canal de adquisición, RGB o tricromática con 3 canales de adquisición, multiespectral con 4-9 canales, hiperespectral con 10 a 100 canales, y ultraespectral con más de 100 canales de adquisición. Independientemente del número de canales utilizado en una aplicación específica, el principio de captación de información es similar, en el cual se emplea un dispositivo de captura pancromático (absorbiendo longitudes de onda en todo el espectro visible y parte de infrarrojo cercano), precedido por una serie de filtros para percibir solo las bandas espectrales de interés.

Hasta ahora, los sistemas Multiespectrales Aerotransportados manejados por las instituciones venezolanas han sido analógicos. Sin embargo, con el desarrollo de la electrónica de estado sólido, las tendencias mundiales de estos sistemas han migrando hacia herramientas digitales. En el mercado existen sistemas multiespectrales aerotransportados comerciales, pero estos tienen un alto costo y son de tecnología totalmente cerrada, lo cual conlleva a los institutos geográficos a depender de estas empresas fabricantes, traduciéndose esto en costos aún mayores.

Una vez realizadas las primeras investigaciones sobre el tema, se planteó dividir el proyecto en varios módulos, entre los cuales están: sistema de adquisición y almacenamiento de imágenes, sistema de georeferenciación, sistema de estabilización de la plataforma soporte y sistema de pre y post procesamiento de las imágenes capturadas

En este sentido, el objetivo principal de este trabajo es presentar resultados parciales del diseño y desarrollo de un sistema de adquisición de imágenes pancromáticas georeferenciadas, en el cual se exponen imágenes de alta resolución espacial e información asociada a magnitudes de posicionamiento y desplazamiento del medio soporte, almacenadas en formato digital para su posterior procesamiento.

En las siguientes secciones se explicará en detalle el desarrollo de la tarjeta de captura de imágenes empleando un sensor de tecnología basada en Semiconductor de Óxido Metálico Complementario (CMOS), la implementación del hardware para el control de los diversos recursos del sistema a través de un dispositivo de Arreglo de Compuertas Programables en Campo (FPGA), la integración de los dispositivos de medida para los datos de georeferenciación, los resultados obtenidos y los diversos aspectos encontrados como puntos de mejora para continuar con el desarrollo del sistema.

II. Arquitectura del sistema

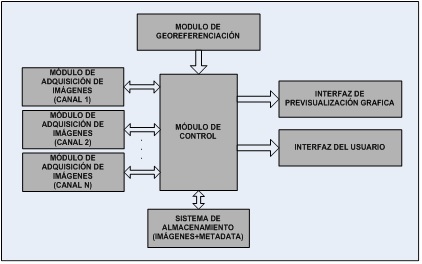

La arquitectura del sistema constituye la estructura básica mediante la cual se desarrollaron las diversas etapas de este trabajo. Una vez revisado la literatura de diversos sistemas de captura de imágenes se decidió establecer una serie de módulos, en los cuales se engloban los requerimientos necesarios para este desarrollo.

En la Fig. 1 se presenta un esquema conceptual de los módulos que integran el sistema de adquisición de imágenes georeferenciadas.

Dentro de los requerimientos planteados en una primera etapa se contempló, por módulo:

- Adquisición de Imágenes: Selección de un sensor CCD o CMOS y manejo de las señales asociadas a éste para su control.

- Georeferenciación: Selección de un dispositivo capaz de medir variables inerciales (IMU) y de posicionamiento global (GPS), con interfaz de comunicación para integrarlo al módulo de control principal.

- Previsualización Gráfica: Representación en alguna interfaz gráfica (monitor, display LCD, etc.) la información percibida en el sensor de imagen, durante la etapa de diseño.

- Control: Selección de algún dispositivo programable para el control de los diversos módulos, con capacidad de procesamiento concurrente y de alta velocidad (orden de los MHz)

- Interfaz del Usuario: Implementación de una aplicación en una PC, con algún lenguaje de programación de alto nivel (C++, Labview, Visual Basic, etc.), para realizar funciones de configuración y control de los recursos, así como la interpretación de datos a obtener de los diversos sensores. Esta interfaz debe permitir conectividad hacia recursos periféricos en la PC para comunicación con el módulo de control del sistema.

- Almacenamiento: Selección de un dispositivo y/o medio de almacenamiento de información masiva y continua, entre las cuales están las imágenes de alta resolución y los parámetros de georeferenciación. En una primera etapa, a modo de pruebas, este módulo estará integrado en una PC junto al de interfaz de usuario.

En las siguientes líneas se plantea con mayor detalle los procedimientos de diseño y desarrollo empleados en cada módulo.

Módulo de adquisición de imágenes

EL módulo de adquisición de imágenes está formado básicamente por tres elementos: el sensor, la óptica y la tarjeta de circuito impreso para actuar como interfaz con los otros módulos.

A. Sensor de Imagen

Para realizar la captura de imágenes se utilizó un sensor electrónico de tecnología CMOS como elemento principal, el cual consiste en un dispositivo de estado sólido capaz de detectar luz, dentro de un amplio rango espectral, para transformarla en señales eléctricas [2]. La tecnología del sensor empleado fue seleccionada luego de realizar una evaluación técnica entre los dos principales tipos de sensores de imagen (CMOS vs. CCD) [3], y una revisión de diversos fabricantes.

El dispositivo escogido para el sistema es el IBIS4-6600 monocromático, de ON Semiconductor (antes Cypress Semiconductor) que integra la adquisición completa de la imagen analógica, un digitalizador y un sistema de procesamiento de señales digitales en un sólo encapsulado [4]. Este sensor posee una resolución de 6.6Mpixeles dispuestos en un arreglo matricial de 2.210 x 3.002 píxeles activos. Cada píxel posee una arquitectura interna conocida como píxel de tres transistores o 3T, la cual permite realizar el reset del mismo, además del direccionamiento de las filas y columnas para la lectura de información en cada píxel. Finalmente, el sensor posee una etapa común de acondicionamiento de señales, formada por amplificadores y convertidores analógico/digital (ADC), que permiten obtener la información de cada píxel digitalizada en una palabra de 10 bits.

La frecuencia de operación máxima del sensor CMOS es de 40MHz, con la cual se logra obtener hasta 5 imágenes por segundo a máxima resolución; esta tasa puede aumentar al variar el tamaño de la imagen mediante una ventana de interés, o bien realizando un submuestreo de los píxeles activos, ambas cualidades programables por el usuario. Cada píxel posee un área de 3.5µm x 3.5µm, lo que genera un área óptica efectiva total de 7,74mm x 10,51mm. El disparo en cada captura es de tipo electrónico y la exposición para realizar el muestreo de la cantidad de luz percibida se realiza línea por línea, lo cual se conoce como formato tipo persiana o Rolling Shutter. Existen otros sensores que cuentan con este mismo formato, pero además pueden realizar la exposición de todas sus líneas simultáneamente, lo que se conoce como disparo global o Global Shutter.

Para operar el sensor se configuran un conjunto de registros mediante el protocolo de Interfaz Serial-Paralela (SPI) de tres hilos. Entre los registros para la configuración de la imagen están: número de filas, número de columnas, región de interés, píxel de origen de la imagen, tipo de submuestreo, etc.; igualmente, existe la posibilidad de controlar digitalmente parámetros de las etapas de acondicionamiento de señales, tales como ganancias, niveles de referencia y/o ajuste, entre otros.

Una vez configurado el dispositivo se ejecuta la lectura de los datos que forman las imágenes. Para esto se generan señales de sincronismo horizontal, desde la tarjeta de control, con lo que se obtienen los datos píxel tras píxel, y sincronismo vertical para efectuar los cambios de línea. Para verificar el correcto funcionamiento de las tramas de configuración y de los pulsos de sincronismo en la lectura, se utilizó un osciloscopio digital de alta velocidad, lo que permitió analizar, verificar y corregir los datos enviados a los registros del sensor, así como los pulsos de control enviados para el barrido y las señales de confirmación generadas por éste.

B. Óptica

Para la selección de la lente se realizó un estudio previo [5] de los factores que influyen en la calidad de la imagen que incidirá sobre el sensor CMOS. En este trabajo se analizaron los parámetros de distancia focal, el diámetro de apertura y el número f o f/#, qué representa cada uno y cómo influyen éstos al realizar la captura de imágenes con el sensor seleccionado y diversos lentes.

Actualmente se está utilizando una lente comercial marca Canon, modelo EF-28mm, con un número f/2.8. Esta lente ha permitido realizar captura de imágenes a modo de prueba, con lo cual se ha logrado manejar los diversos parámetros del sensor, y corregir los efectos por ruido y distorsión que se producen inicialmente en las imágenes.

Para integrar la tarjeta del sensor con la lente seleccionada se fabricó una caja de plástico, a la cual se le adaptó un anillo metálico ajustable, a fin de poder colocar lentes intercambiables. Para ello fue necesario considerar como parámetro de diseño la Distancia Focal de Brida (FFD), la cual es la longitud que existe entre el borde de la lente y la superficie óptica del sensor CMOS. Para el caso de la lente Canon seleccionada, el factor FFD es de 44mm [6]. Este factor varía para diversos tipos y/o fabricantes de lentes, pero en nuestro caso, como el anillo soporte se diseño para que pueda ser ajustable, el sistema puede utilizar cualquier otra lente que sea de conveniencia.

En el sistema de la cámara multiespectral, la selección de la lente dependerá de qué resolución espacial se necesite en la aplicación, a qué altura se realice el vuelo y cuánto terreno se desea abarcar en cada toma. En este sentido, mientras mayor sea la distancia focal, la resolución espacial será mayor; en este caso, habrá que tomar más imágenes para cubrir la misma área que se abarcaría si se realizara la captura con una lente de menor distancia.

C. Tarjeta de Circuito Impreso para el manejo del Sensor CMOS

Para integrar el sensor al resto del sistema se desarrolló una Tarjeta de Circuito Impreso (PCB) con la cual se ejecutó la configuración de los parámetros iniciales y lectura de los datos generados en la captura.

El diseño del PCB se realizó en la FII, y consistió en la elaboración del circuito esquemático, (considerando las etapas de alimentación, regulación y niveles de referencia), la conexión de los diversos pines del sensor, los componentes necesarios para el desacople de señales no deseadas en el circuito y la distribución de los pines de entrada/salida para interconectar la tarjeta con el resto del sistema. Posteriormente se realizó el enrutamiento de los circuitos y se generaron los archivos Gerbers para la construcción del PCB. El enrutamiento del PCB se realizó en cuatro capas. Finalmente, se realizaron las pruebas eléctricas al PCB (verificando la continuidad en las vías o pads de interconexión entre capas, y que no exista cortocircuito entre los puntos de alimentación y tierra), el montaje de los componentes y conectores, y las pruebas funcionales.

Módulo de georeferenciación de imagenes

Para realizar la georeferenciación de las imágenes, el sistema utiliza un sensor MTi-G fabricado por Xsens [7]. Este dispositivo integra un GPS y una Unidad de Medida Inercial (IMU), basado en sensores inerciales MEMS (Sistema Micro-electro-mecánico), un receptor GPS miniatura y sensores auxiliares (barómetro, y magnetómetros en X, Y y Z). El MTi-G cuenta con un DSP y una memoria flash para el procesamiento de los datos y el almacenamiento de los parámetros de configuración. La Fig. 2 muestra la arquitectura interna del dispositivo y un diagrama de conexiones típico.

Entre las variables que se pueden obtener del sensor están: los datos propios de un GPS (latitud, longitud, altitud, presión, estado de los satélites, etc.), las variables de orientación, conocidas como ángulos de navegación o ángulos de Euler (Roll, Pitch, Yaw), los datos de calibración (aceleración, velocidad angular, campo magnético), los datos de velocidad de desplazamiento (en los ejes X, Y y Z) y la estampa de tiempo de las muestras en formato UTC. Cada uno de estos grupos de variables está representado en una estructura de datos digitales de diferentes magnitudes, los cuales en conjunto forman una trama de datos de 116bytes.

El MTi-G posee dos modos de trabajo. El primero es de configuración, en el cual se definen los parámetros iniciales (frecuencia de muestreo, velocidad de transmisión de los datos, grupos de variables a muestrear, entre otros). El segundo modo es de medición, en el cual el dispositivo realiza el muestreo de los diversos sensores internos y los transmite hacia algún equipo o módulo externo.

Por otra parte, el MTi-G genera un pulso de sincronismo a partir de su reloj interno; esta señal llamada SyncOut marca el instante de tiempo con el cual el sensor inicia el muestreo de las variables seleccionadas. Este proceso se repite periódicamente a la frecuencia de SyncOut, proporcional a la frecuencia de muestreo, mientras que el MTi-G se encuentre en modo de medición. Cada vez que se genera este pulso de sincronismo, los datos de las variables son transmitidos por una interfaz serial hacia un módulo externo, a una tasa (ajustable) proporcional a la frecuencia de muestreo.

Módulo de Control

Después de evaluar los módulos de adquisición de imágenes y de obtención de datos geográficos, se procedió a definir el dispositivo lógico programable más adecuado para realizar el control de los recursos y el manejo de los datos. Entre las posibles opciones estaban: un microcontrolador, un Procesador Digital de Señales (DSP) o un FPGA. Al realizar la evaluación entre las ventajas y desventajas que ofrecen cada uno de éstos, se decidió trabajar con el FPGA, entre otras cosas por su capacidad de manejar procesos concurrentes (paralelos) y totalmente independientes, y por la practicidad al definir o redefinir arquitecturas del hardware para acelerar algún algoritmo. Los otros dispositivos pueden generar un pseudo-paralelismo, pero siempre terminan ejecutando un desarrollo secuencial. Asimismo, la FPGA maneja niveles de bajo voltaje (3.3v) lo que permite compatibilidad entre este elemento y el sensor de imágenes.

Una vez seleccionada la tecnología FPGA, se procedió a definir detalladamente la arquitectura a utilizar en el sistema, en función de los recursos necesarios y disponibles para manejar la tarjeta de captura de imágenes y el canal de transmisión hacia el sistema de almacenamiento. La programación se realizó bajo el lenguaje de descripción de hardware (VHDL), de cada una de las entidades de control de los recursos disponibles.

- Arquitectura del Hardware en FPGA

Para el implementar la arquitectura del sistema se seleccionó un kit de desarrollo DE2-70 de TERASIC, basado en el FPGA tipo Cyclone II EP2C70de ALTERA [8]. Ésta tarjeta cuenta con todos los recursos necesarios, establecidos en los requisitos del diseño conceptual. Además, dicho kit de desarrollo, por ser aplicado con fines de investigación, fue adquirido a un precio accesible.

La Fig. 3 muestra un esquema en bloques detallado de la arquitectura implementada, en base a los recursos disponibles en la tarjeta de desarrollo.

Los módulos de la tarjeta DE2-70 utilizados para el sistema son:

- La memoria síncrona dinámica de acceso aleatoria (SDRAM) de 32Mbyte de capacidad, distribuida en 4 bancos de 8Mbytes cada uno, con manejo de palabras de 16 bits de ancho. En ésta se realiza el almacenamiento momentáneo de los datos recibidos desde el sensor CMOS.

- Los dos puertos de propósito general (GPIO), los cuales agrupan un conjunto de pines con acceso directo al FPGA para interconectar periféricos o módulos externos.

- La interfaz para el Adaptador Grafico de Video (VGA), con la cual se previsualiza la escena captada por el sensor, antes de ejecutar el almacenamiento de datos. Esta interfaz se configuró con un formato SVGA 800×600 a 60Hz, para un reloj de píxel de 40MHz.

- El puerto serial RS-232 para interconectar el sensor IMU/GPS al sistema y poder captar los datos de georeferenciación.

- El puerto USB con manejo del estándar JTAG, con el cual se transmite la síntesis de los programas descritos desde la PC hacia la memoria interna del FPGA.

- La FPGA para desarrollar toda la descripción de los circuitos complementarios y lógica de los procesos de control de los recursos.

Como se observa en la Fig. 3, en uno de los puertos GPIO se conectó la tarjeta de adquisición de imágenes; este factor de compatibilidad entre los pines de ambas tarjetas ya había sido considerado durante el diseño de la PCB del sensor CMOS. En el otro puerto GPIO se conectó un módulo FT2232H de FTDI [9], el cual permite establecer una interfaz de comunicación entre el sistema y una PC, a través del protocolo USB 2.0 High Speed. Si bien la tarjeta de desarrollo cuenta con un bus USB 1.1 Full Speed, la velocidad de esta interfaz (60Mbits/s) no es adecuada para realizar la transmisión de los datos de la aplicación, por la baja tasa de baudios.

Por otra parte, para conectar la señal SyncOut desde MTi-G al sistema de control se utiliza un pin del puerto GPIO. La transmisión de los datos se realizó mediante una pequeña tarjeta interfaz que se construyó, la cual permitió conectar dicho sensor con los pines Tx y GND del puerto serial DB-9 en la tarjeta de desarrollo. En la tarjeta se incorporó un regulador de tensión de 5V DC, para alimentación del MTi-G.

- Desarrollo del Programa en VHDL

Para realizar la implementación de los circuitos de control de los recursos del sistema y su lógica de operación, se realizó la programación en VHDL. Este es un lenguaje de descripción de hardware utilizado para describir circuitos digitales. Fue diseñado por la IEEE [10] en base a los principios de la programación estructurada.

En cuanto al desarrollo de la arquitectura del sistema, la etapa de programación fue desarrollada bajo el software Quartus II v 9.0. Este software es el adecuado para trabajar sobre el tipo de FPGA seleccionado, ya que su fabricante también es ALTERA y puede ser adquirido (con restricciones) gratuitamente en la versión tipo web. De la misma forma, durante la programación se utilizó la metodología Top-down, para la cual se definió una estructura de hardware general, y posteriormente se desarrollaron los detalles internos de cada uno de los bloques que la conforman.

De acuerdo a esta metodología, para el desarrollo del programa en VHDL se ejecutaron los siguientes pasos:

- Construcción de un diagrama de bloques del sistema, considerando los elementos internos del FPGA, los buses y recursos.

- Elaboración de los códigos en VHDL para cada entidad o bloque y para sus interfaces.

- Compilación de los códigos una vez desarrollada la descripción de los procesos de cada entidad.

- Construcción de los vectores de las señales para la simulación, en el cual se establecen los estímulos a cada componente.

- Simulación del comportamiento de los circuitos y sus respuestas. La simulación busca evaluar el funcionamiento del hardware descrito, más que verificar entradas y salidas del mismo.

- Rediseño de las entidades a partir de los resultados esperados y las respuestas obtenidas.

Para el desarrollo de los bloques que controlan los procesos de adquisición de imágenes, visualización, georeferenciación y almacenamiento de datos, se planteó el diagrama de bloques que se ilustra en la Fig. 4.

Se puede observar que la descripción del hardware desarrollado dentro del FPGA está compuesta por: el generador de señales para configuración y lectura del sensor de imágenes, el controlador de la lectura, escritura y configuración de la memoria de SDRAM, el manejador de interfaz gráfica VGA, el manejador de protocolo del bus USB, el control del puerto RS-232 para la lectura del sensor de georeferenciación IMU/GPS, y el bloque de control principal de todos los recursos.

Internamente en el diagrama se pueden observar los buses de datos, control y direccionamiento, establecidos entre cada uno de los componentes. Dentro de cada uno de los bloques presentados, se desarrollo en código VHDL la descripción de los procesos asociados a cada recurso. Para esto se estudió previamente el principio de funcionamiento, las señales de sincronismo, las temporizaciones y las estructuras de datos de cada chip y/o módulo que se utilizó en el kit de desarrollo y de sus tarjetas complementarias.

Interfaz del Usuario

La interfaz de usuario en la PC se desarrolló bajo el software Labview 2010 de National Instrument. En la aplicación se ejecutan funciones de control, ajuste y visualización, entre las cuales están: reset general de los dispositivos del FPGA, configuración de los registros del sensor CMOS, orden de captura y transmisión de la imagen vía USB, definición del formato y ruta de almacenamiento para los archivos de imagen y de datos de georeferenciación, previsualización de la imagen y gráfico de histogramas de los datos recibidos. Esta aplicación está construida con una estructura básica ya que, hasta la fecha, se ha concentrado la atención en el desarrollo de la arquitectura de hardware en la FPGA.

La Fig. 5 muestra una vista del panel frontal de la aplicación desarrollada en Labview.

La transmisión de parámetros de configuración (PC → FPGA) y los datos de imagen y metadata (FPGA → PC) se realiza a través del bus USB, mediante un módulo FT2232H conectado a la tarjeta de desarrollo de ALTERA. El estándar utilizado para esto es USB v2.0 High Speed, con una velocidad máxima de 480Mbits/s y un modo de transmisión tipo ráfaga o Burst. Para poder manejar este dispositivo desde la aplicación, se instalaron los controladores y las librerías proporcionadas por el fabricante. Estas librerías son compatibles con el software de Labview y permitieron ejecutar una serie de comandos directos sobre el manejador del puerto USB. Asimismo, existen otras librerías que pueden ser integradas a otros lenguajes de programación como lo son C++, C#, Visual Basic, entre otras.

III. Funcionamiento General del Sistema

En la primera fase se ejecuta el proceso de configuración, en el cual se inicializan: la memoria SDRAM, los registros del sensor CMOS, los parámetros del puerto de comunicación serial y los registros del bus de comunicaciones USB. Los parámetros iniciales cargados al sensor de imagen están definidos, por defecto, dentro de la descripción en VHDL.

Configurado el sistema se procede a la etapa de captura. En este caso, el bloque de control principal emite una señal de sincronización general para la lectura del sensor de imagen, con lo cual se almacenan temporalmente en la memoria SDRAM los datos obtenidos, mientras que los datos de georeferenciación son guardados temporalmente en un arreglo interno del FPGA. El pulso de sincronismo general está asociado directamente a la señal SyncOut proveniente del MTi-G. Esta señal está configurada a una frecuencia de 20Hz, lo que permite al control principal realizar la captura en escalas de tiempo múltiplos de 50ms. En particular, como se definió un disparo cada 1s se cuentan 20 pulsos del SyncOut. Adicionalmente, la tasa de muestreo de los sensores inerciales del MTi-G es de 120Hz, por lo cual entre dos pulsos de SyncOut, la FPGA recibe seis tramas de datos de georeferenciación, lo cual permite al sistema principal obtener una nueva trama de datos si detecta errores en la recibida previamente.

Seguidamente, durante la etapa de previsualización, el control principal ordena extraer los datos de la memoria SDRAM y los envía hacia la interfaz gráfica VGA, para mostrar la imagen en un monitor. Esto se realiza periódicamente a una tasa de muestreo (actualmente 1 imagen por segundo), en el intervalo de tiempo disponible entre las lecturas del sensor CMOS.

Posteriormente, durante la etapa de transmisión, el usuario emite un comando de captura desde la aplicación en Labview hacia el sistema para comenzar a recibir los datos. En ese instante el control principal genera una interrupción y comienza a enviarse la estructura de datos de georeferenciación e imagen a través del bus USB hacia la PC

Finalmente, durante la etapa de almacenamiento, la aplicación en Labview toma la estructura de datos y los separa: por una parte se guarda en un archivo de texto los datos de georeferenciación, mientras que en otro archivo se escriben los datos de las imágenes recibidas. Este último puede ser almacenado en un formato propio de la aplicación (RAW), o bien, en un formato estándar de imagen (BMP, TIFF, JPEG, PNG).

IV. Pruebas y Resultados

Una vez culminados los procesos de simulación y programación de la FPGA, se procedió a verificar las señales de barrido y lectura del sensor CMOS en tiempo real. Para ello se utilizó un osciloscopio Tektronik MSO-4054. La Fig. 6 muestra un fragmento de tiempo observado en los pines de sincronismo de línea (Y-Clock)y de validez de los datos (Píxel Valid) durante la lectura de información del sensor CMOS.

Posteriormente, se obtuvieron imágenes de previsualización de la escena a través de un monitor conectado a la salida de interfaz gráfica VGA de la tarjeta de desarrollo. La Fig. 7 presenta una fotografía de lo antes descrito.

Mediante el software MT Manager, suministrado por el fabricante, se configuró el sensor MTi-G. Seguidamente se realizaron pruebas de comunicación entre el dispositivo y el puerto serial en la PC para verificar la validez de las tramas de datos. Esta verificación se dividió en dos partes: comprobación del encabezado de la trama (PREh+ BIDh + MIDh + LENh=FA FF 32 74) [11] y verificación del CheckSum (CS). Si el encabezado no era el correcto o el CS estaba errado, se asumía que la trama no era válida.

La Fig. 8 muestra las tramas de los datos de georeferenciación, obtenidas en el software analizador de protocolo EasyCom.

A continuación se procedió a transmitir los datos directamente hacia el sistema, por medio del puerto serial RS-232 de la tarjeta de desarrollo. La comprobación de los datos se realizó siguiendo el mismo procedimiento de la prueba anterior, pero directamente con las tramas recibidas en la interfaz de usuario.

Finalmente, para evaluar la captura de imágenes desde la interfaz en Labview, se tomaron varias imágenes de una misma escena, variando manualmente los parámetros de ganancia, offset y tiempo de integración, observando la influencia de cada uno de éstos en la calidad de las imágenes. En la Fig. 9 se presentan tres imágenes tomadas (lado izquierdo) de una misma escena, con su respectivo gráfico de histogramas (lado derecho), con ajuste de ganancia distintos.

V. Conclusiones y Recomendaciones

Durante este trabajo se creó un sistema de adquisición de imágenes, implementado a partir de la integración y el manejo de diversos dispositivos, entre los cuales destacan: un sensor de imágenes CMOS, un sensor de georeferenciación IMU/GPS, un circuito de control diseñado sobre un FPGA y una interfaz de comunicación con una PC mediante el protocolo USB. Como se ha mencionado, este sistema constituye una arquitectura base para el diseño y desarrollo del “Sistema de Cámara Multiespectral Aerotransportada”. Además, este prototipo puede ser tomado como punto de partida para el desarrollo de otros proyectos relacionados con Captura de Imágenes y/o Sistemas de Visión Artificial.

La cualidad de paralelismo de la FPGA permitió ejecutar procesos concurrentes en tiempo real, lo que en este proyecto es una condición fundamental, tratándose de un sistema complejo con manejo simultáneo de recursos de hardware.

La arquitectura de control en el FPGA se planteó satisfactoriamente, pasando de unas primeras pruebas de tomas de imágenes con resolución de 800×600 píxeles a una lectura y transferencia de fotos a mayor resolución (6.1MPixeles aproximadamente), ajustable por el usuario, logrando almacenar éstas en un disco duro bajo un formato de imagen conocido (BMP, TIFF, PNG) o en un formato particular del sistema (RAW). Este paso es fundamental para realizar el post-procesamiento de los datos en las próximas etapas del proyecto.

Si bien se logró aumentar el tamaño de la imagen leída por el sensor CMOS en las diversas pruebas, no se llegó a alcanzar su máxima resolución (6.6MPixeles), ya que al realizar el proceso de escritura en la memoria disponible en la tarjeta de desarrollo, por su estructura interna y por la descripción implementada en VHDL, no se alcanzó a muestrear el total de las columnas disponibles de cada línea del sensor de imagen.

La resolución de la imagen podrá aumentar si se incluyen en futuros diseños de la tarjeta de control, una memoria SDRAM con una estructura similar a la utilizada actualmente, pero con mayor número de bancos, o con mayor capacidad de columnas en sus líneas, a fin de aprovechar la descripción de hardware ya implementada.

De acuerdo a las imágenes obtenidas en las primeras pruebas, y a las bibliografías consultadas sobre efectos naturales de ruido y distorsión producidos en estos sensores, queda como trabajo futuro establecer procedimientos para la calibración del sensor CMOS, así como otros procesos de ajuste de sensibilidad, de brillo y contraste antes y durante la exposición. Estas rutinas ya han comenzado a ser evaluadas y se ha observado que existe una relación directa entre los parámetros tales como: ganancia, offset, tiempo de integración y balance de los canales de conversión A/D, para tener una relación entre dichas variables.

Posteriormente, a la hora de ejecutar la exposición y captura de las imágenes se deberá tomar una primera muestra, a fin de evaluar las condiciones de iluminación y contraste de la escena, para finalmente reajustar los parámetros antes mencionados y obtener una imagen óptima. El ajuste al momento de la exposición se deberá hacer bien sea imagen por imagen, si está en un modo automático, o bien, sólo al inicio de la captura de una secuencia de fotos.

Referencias Bibliográficas

- J.Y. Hardeberg, F. Schmitt, H. Brettel, J.P. Crettez y H. Maître, «Multispectral Image Acquisition and Simulation of Illuminant Changes», en L.W. MacDonald y M.R. Luo (eds.), Colour Imaging: Vision and Technology, John Wiley and Sons, New York 1999.

- J. Nakamura “Image Sensors And Signal Processing for Digital Still Cameras” Ed. CRC Press, 2006, pp 62.

- J. Ulloa, “Sensores de Imagen para Cámaras Digitales”. Nota de Ingeniería, Unidad de Tecnología Electrónica Industrial, Fundación Instituto de Ingeniería, Baruta, 2009.

- Datasheet: “6.6 MP CMOS Image Sensor”. Cypress Semiconductor Corporation, San Jose, CA, April 2010.

- J. Salazar, “Parámetros Ópticos en Sistemas de Captura de Imágenes”. Nota de Ingeniería, Unidad de Tecnología Electrónica Industrial, Fundación Instituto de Ingeniería, Baruta, 2009.

- Wikipedia (Consulta en julio, 2009) “Flange focal distance”. Disponible en http://en.wikipedia.org/wiki/Flange_focal_distance.

- MTi-G User Manual and Technical Documentation. Xsens Technologies B.V., May 2009.

- User Manual: “DE2-70 Develop and Education Board”. Terasic Technologies, 2007.

- Datasheet: “USB High Speed FT2232H Evaluation Module”. Future Technology Devices International Ltd (FTDI). Glasgow, January 2011.

- IEEE Standard VHDL, Language Reference Manual. IEEE Std 1076, New York 2000.

- Y. Sanjuan, “Parámetros de Georeferenciación en Sistemas de Captura de Imágenes”. Nota de Ingeniería, Unidad de Tecnología Electrónica Industrial, Fundación Instituto de Ingeniería, Baruta, 2009.

Contactos: tomasenriqueramosmesa@gmail.com ; ma.arellanob@gmail.com